|

ARMEBS4

revision-26.06.2015

|

|

ARMEBS4

revision-26.06.2015

|

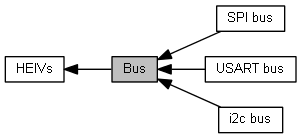

Bus abstraction layer. More...

|

Modules | |

| SPI bus | |

| SPI (Serial Peripheral Interface) bus. | |

| USART bus | |

| USART (Universal Synchronous Asynchronous Receiver Transmitter) bus.USART or UART implements the RS232 specification. | |

| i2c bus | |

| i2c bus. | |

Data Structures | |

| struct | heivs_bus_var_t |

| Variable part of the bus description. More... | |

| struct | heivs_bus_t |

| Bus handler. More... | |

Macros | |

| #define | BUS_PARANOIA |

Enumerations | |

| enum | heivs_bus_state_t { BUS_NOINIT, BUS_INACTIVE, BUS_ACTIVE, BUS_SUSPENDED } |

| State of the bus. More... | |

Functions | |

| status_e | bus_init (const struct heivs_bus_t *bus) |

| initialize the bus More... | |

| status_e | bus_get (const struct heivs_bus_t *bus) |

| Get exclusive access to the bus. More... | |

| status_e | bus_release (const struct heivs_bus_t *bus) |

| Release exclusive access to the bus. More... | |

| status_e | bus_suspend (const struct heivs_bus_t *bus) |

| Suspend the bus (low power mode) More... | |

| status_e | bus_resume (const struct heivs_bus_t *bus) |

| Resume the bus (from low power mode) More... | |

| status_e | bus_read (const struct heivs_bus_t *bus, uint32_t address, void *data, size_t len, size_t *rlen) |

| Resume the bus (from low power mode) More... | |

| status_e | bus_write (const struct heivs_bus_t *bus, uint32_t address, const void *data, size_t len) |

| Write data to the bus. More... | |

| status_e | bus_writeread (const struct heivs_bus_t *bus, uint32_t address, const void *src, size_t src_len, void *dst, size_t dst_len, size_t *rlen) |

| Combined write and read data. More... | |

Bus abstraction layer.

This abstraction will be used to hide bus (i2c, spi, ...) behind a easy to use interface

| enum heivs_bus_state_t |

State of the bus.

| Enumerator | |

|---|---|

| BUS_NOINIT |

Bus never initialized Choosen value is zero because C uninitialized variables are zeros

|

| BUS_INACTIVE |

Initialized, but free to use

|

| BUS_ACTIVE |

In use

|

| BUS_SUSPENDED |

Low power mode, use bus_init to re-enable

|

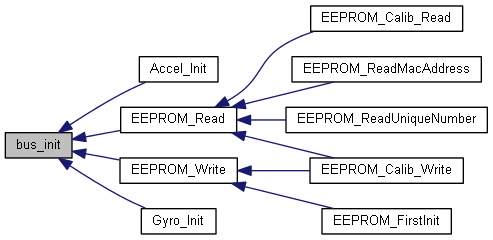

| status_e bus_init | ( | const struct heivs_bus_t * | bus | ) |

initialize the bus

| bus |

Definition at line 59 of file bus.c.

References heivs_bus_t::_init, BUS_ACTIVE, BUS_INACTIVE, BUS_NOINIT, NO_ERROR, and heivs_bus_t::var.

Referenced by Accel_Init(), EEPROM_Read(), EEPROM_Write(), and Gyro_Init().

| status_e bus_get | ( | const struct heivs_bus_t * | bus | ) |

Get exclusive access to the bus.

| bus |

Definition at line 134 of file bus.c.

References BUS_ACTIVE, BUS_INACTIVE, ERROR_BUS_BAD_STATE, NO_ERROR, and heivs_bus_t::var.

Referenced by Accel_Read(), Accel_WriteCfg(), EEPROM_Read(), EEPROM_Write(), Gyro_RD(), Gyro_Read(), Gyro_Write(), reg_read(), and reg_write().

| status_e bus_release | ( | const struct heivs_bus_t * | bus | ) |

Release exclusive access to the bus.

| bus |

Definition at line 149 of file bus.c.

References BUS_ACTIVE, BUS_INACTIVE, ERROR_BUS_BAD_STATE, NO_ERROR, and heivs_bus_t::var.

Referenced by Accel_Read(), Accel_WriteCfg(), bus_read(), bus_resume(), bus_suspend(), bus_write(), bus_writeread(), EEPROM_Read(), EEPROM_Write(), Gyro_RD(), Gyro_Read(), Gyro_Write(), reg_read(), and reg_write().

| status_e bus_suspend | ( | const struct heivs_bus_t * | bus | ) |

Suspend the bus (low power mode)

| bus |

This function will disable the bus controller, put all pins used to logical level zero to prevent power leakage.

The bus must be owned (bus_get) before suspend and can be resumed using bus_resume

Definition at line 163 of file bus.c.

References heivs_bus_t::_suspend, bus_release(), BUS_SUSPENDED, NO_ERROR, and heivs_bus_t::var.

| status_e bus_resume | ( | const struct heivs_bus_t * | bus | ) |

Resume the bus (from low power mode)

| bus |

Definition at line 180 of file bus.c.

References heivs_bus_t::_resume, BUS_ACTIVE, bus_release(), NO_ERROR, and heivs_bus_t::var.

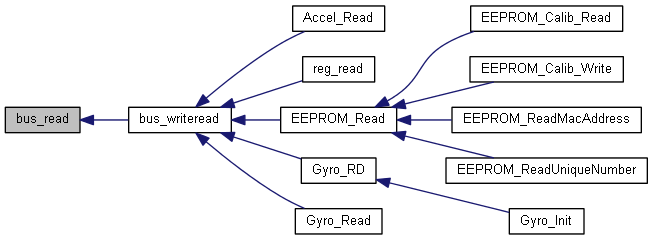

| status_e bus_read | ( | const struct heivs_bus_t * | bus, |

| uint32_t | address, | ||

| void * | data, | ||

| size_t | len, | ||

| size_t * | rlen | ||

| ) |

Resume the bus (from low power mode)

| bus |

| bus | |

| address | for i2c, the chip address, unused for spi and uart |

| data | buffer where the data will be stored |

| len | buffer len |

| rlen | effective count of read bytes, can be NULL if not interested |

Definition at line 198 of file bus.c.

References heivs_bus_t::_read, BUS_ACTIVE, bus_release(), ERROR_BAD_PARAM, and NO_ERROR.

Referenced by bus_writeread().

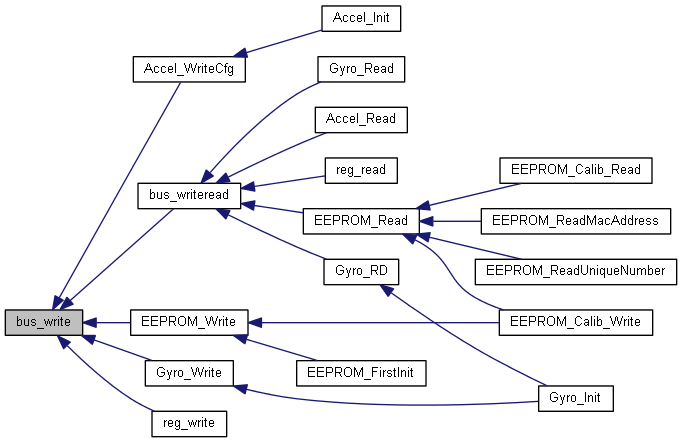

| status_e bus_write | ( | const struct heivs_bus_t * | bus, |

| uint32_t | address, | ||

| const void * | data, | ||

| size_t | len | ||

| ) |

Write data to the bus.

| bus | |

| address | for i2c, the chip address, unused for spi and uart |

| data | to be sent |

| len | of data |

Definition at line 243 of file bus.c.

References BUS_ACTIVE, bus_release(), ERROR_BAD_PARAM, and NO_ERROR.

Referenced by Accel_WriteCfg(), bus_writeread(), EEPROM_Write(), Gyro_Write(), and reg_write().

| status_e bus_writeread | ( | const struct heivs_bus_t * | bus, |

| uint32_t | address, | ||

| const void * | src, | ||

| size_t | src_len, | ||

| void * | dst, | ||

| size_t | dst_len, | ||

| size_t * | rlen | ||

| ) |

Combined write and read data.

| bus | |

| address | for i2c, the chip address, unused for spi and uart |

| src | data to be sent |

| src_len | len of src |

| dst | data to be read |

| dst_len | len of dst |

| rlen | effective count of read bytes, can be NULL if not interested |

Definition at line 279 of file bus.c.

References BUS_ACTIVE, bus_read(), bus_release(), bus_write(), ERROR_BAD_PARAM, and NO_ERROR.

Referenced by Accel_Read(), EEPROM_Read(), Gyro_RD(), Gyro_Read(), and reg_read().

1.8.9.1

1.8.9.1