|

ARMEBS4

revision-26.06.2015

|

|

ARMEBS4

revision-26.06.2015

|

Digital to Analog Converter. More...

#include "C:/Programs/ARMEBS4/current/doc/eclipse-doc/ext/libheivs_stm32/include/stm32/stm32f4xx.h"

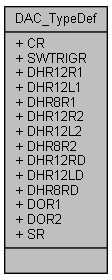

Data Fields | |

| __IO uint32_t | CR |

| __IO uint32_t | SWTRIGR |

| __IO uint32_t | DHR12R1 |

| __IO uint32_t | DHR12L1 |

| __IO uint32_t | DHR8R1 |

| __IO uint32_t | DHR12R2 |

| __IO uint32_t | DHR12L2 |

| __IO uint32_t | DHR8R2 |

| __IO uint32_t | DHR12RD |

| __IO uint32_t | DHR12LD |

| __IO uint32_t | DHR8RD |

| __IO uint32_t | DOR1 |

| __IO uint32_t | DOR2 |

| __IO uint32_t | SR |

Digital to Analog Converter.

Definition at line 407 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::CR |

DAC control register, Address offset: 0x00

Definition at line 409 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::SWTRIGR |

DAC software trigger register, Address offset: 0x04

Definition at line 410 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR12R1 |

DAC channel1 12-bit right-aligned data holding register, Address offset: 0x08

Definition at line 411 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR12L1 |

DAC channel1 12-bit left aligned data holding register, Address offset: 0x0C

Definition at line 412 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR8R1 |

DAC channel1 8-bit right aligned data holding register, Address offset: 0x10

Definition at line 413 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR12R2 |

DAC channel2 12-bit right aligned data holding register, Address offset: 0x14

Definition at line 414 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR12L2 |

DAC channel2 12-bit left aligned data holding register, Address offset: 0x18

Definition at line 415 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR8R2 |

DAC channel2 8-bit right-aligned data holding register, Address offset: 0x1C

Definition at line 416 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR12RD |

Dual DAC 12-bit right-aligned data holding register, Address offset: 0x20

Definition at line 417 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR12LD |

DUAL DAC 12-bit left aligned data holding register, Address offset: 0x24

Definition at line 418 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DHR8RD |

DUAL DAC 8-bit right aligned data holding register, Address offset: 0x28

Definition at line 419 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DOR1 |

DAC channel1 data output register, Address offset: 0x2C

Definition at line 420 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::DOR2 |

DAC channel2 data output register, Address offset: 0x30

Definition at line 421 of file stm32f4xx.h.

| __IO uint32_t DAC_TypeDef::SR |

DAC status register, Address offset: 0x34

Definition at line 422 of file stm32f4xx.h.

1.8.9.1

1.8.9.1